根据FPGA的3GHDSD-SDI信号光纤传输体系的规划

信号经过光纤完结无损长距离传输的办法。与传统的传输计划比较,此计划能够完结传输高清视频的滑润晋级,并向下兼容现有的视频传输网络,下降了网络的改造晋级本钱。

SDI(Serial Digital Interface)是一种“数字重量串行接口”,经过75Ω同轴线缆传输无紧缩的数字视频信号。因为串行数字信号的数据率很高,在传送前有必要经过处理。用扰码的不归零倒置(NRZI)来替代前期的分组编码,其规范为SMPTE 259M和EBU-Tech-3267,规范包含了含数字音频在内的数字复合和数字重量信号,支撑4种速率:143Mbit/s的NTSC制复合编码信号;177.3Mbit/s的PAL制复合编码信号;270Mbit/s的NTSC制和PAL制重量编码信号;360Mbit/s 16:9长宽比的NTSC制和PAL制重量编码信号,其间最常见的是270Mbit/s。在传送前,对原始数据流进行扰频并改换为NRZI码,确保在接纳端可靠地康复原始数据。

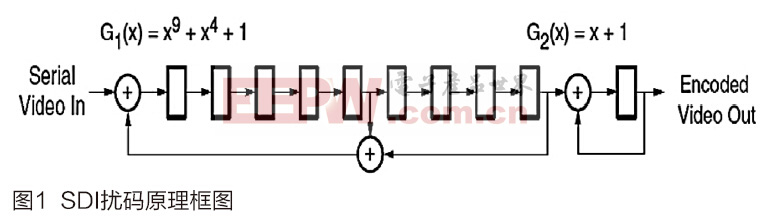

在概念上能够将数字串行接口理解为一种基带信号调制。SDI接口能经过270Mbit/s的串行数字重量信号,关于16:9格局的图画,应能传送360Mbit/s的信号。NRZI码是极性灵敏码。用“1”和“0”表明电平的高和低,假如呈现长期的接连“1”或接连“0”,会影响接纳端从数字信号中提取时钟。因为串行数字信号接口不独自传送时钟信号,接纳端需从数字信号流中提取时钟信号,所以要选用以“1”和“0”来表明有无电平改换的NRZI码。在接纳NRZI码流时,只需检出电平改换,就可康复数据,再经过加扰,连“1”的时机削减,也就使高频重量进一步削减,使解码和提取时钟信息愈加简单。完结加扰/解扰的生成多项式为G1(x)=x9+x4+1,该步首要是将数字化的视频信号变成NRZ扰码信号。编码/译码的生成多项式为G2(x)=x+1,该步首要是将上一步生成的NRZ扰码变成对电平极性不灵敏、只对电平极性改换灵敏的NRZI码。其扰码的原理框图如图1所示。详细完结使用Verilog HDL编程。在接纳端,由SDI解码模块从NRZI码流康复出原数据流。

依照移动图画和电视工程师协会(SMPTE)拟定的清晰度规范要求,SDI可分为:SD-SDI、HD-SDI和3G-SDI。其间:

因为传输的3G/HD/SD-SDI 信号首要用于广播电视职业,其专业级的目标要求,有必要确保输出信号有高稳定性与可靠性。在对信号进行均衡以及

,解扰及串并转化,以及后端的输出驱动的处理过程中,均挑选GENNUM公司的集成电路完结高清视频信号接口的转化,这样做能够最大极限的确保各相关模块的兼容性,而且具有信号康复和颤动按捺功用,体系输出挨近完美的眼图目标,有利于进步体系的稳定性,下降信号的颤动。本体系的主控模块是FPGA,归纳考虑本钱、占用面积以及今后的晋级,就需要FPGA的内部资源尽量丰厚,因而选用Xilinx公司Spartan-3A系列FPGA,该系列FPGA集成了DSP功用,具有极强的并行处理才能,满意图画和视频处理所需的功能要求,包含紧缩(MPEG-2和MPEG-4),色空间转化,图画增强、处理、缩放和辨认等;选用SPI PROM形式完结装备,为便于调试,也预留了JTAG接口; 完结图画收集、存储和整个体系的逻辑操控。

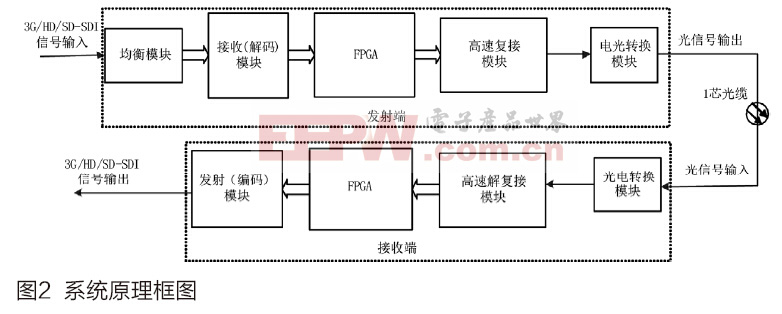

体系分为发射端和接纳端。在发射端,信号先经过均衡、串并转化处理,输入到FPGA完结一次复用后,进入高速复接芯片完结二次复用,最终经电光转化模块将其转化为光信号,这样就将3G/HD/SD-SDI信号转变成光信号。在接纳端,将接纳到的的光信号经光电转化模块转化为电信号,进入高速解复接模块和FPGA中,完结信号解复用和缓存处理后,输入到多速率SDI编码模块,输出原3G/HD/SD-SDI信号。体系原理框图如图2所示。

,信号经过长距离的传输后在线缆中会发生损耗,经过均衡后,信号质量得到显着的改进。在模块输入引脚处衔接75Ω对地电阻进行阻抗匹配。均衡模块对输入信号处理后发生一对差分输出信号,再在两条差分线Ω电阻平衡线间阻抗,将此差分信号输入到多速率SDI接纳模块进行时钟康复和8B/10B解码处理,经串/并转化后发生契合SMPTE 424M/292M/259M规范的20/10bit的并行数据,将此数据送入到FPGA中。数据先缓存在FPGA内部FIFO中,在完结对数据的第一次复用后,复用为10bit的并行数据,输出给高速复接模块,将FPGA输出的低速并行信号复接为高速串行信号,再经过电光转化模块(选用速率为3.125Gbit/s,支撑热插拔的SFP光器材)转化为光信号传输到接纳端。1.2 接纳端

首要将从光缆得到的光信号经过光电转化模块转化成电信号,将此电信号送给高速解复接模块,将高速串行信号进行串并转化处理,将转化后的并行数据输入到FPGA,由FPGA先缓存在内部FIFO中, 再解复用出契合SMPTE 424M/292M/259M规范的20/10bit的并行数据,然后将此并行数据发送给多速率SDI编码模块,从并行数据中提取出时钟,作为采样时钟,对并行数据进行同步处理,一起提取出图画数据和图画格局信息,完结3G/HD/SD-SDI信号的8B/10B编码,最终输出到接纳设备,完结了3G/HD/SD-SDI信号的

- 上一篇:光纤通讯体系(共83张PPT)

- 下一篇:光通讯的开展现状怎么样?